# PNX8526 Reg. Summary List AN10263\_1

Programmable Source Decoder with Integrated Peripherals

Rev. 01 — 8 October 2003

**Revision History:**

| Version | Date           | Document Status | Author(s)       |

|---------|----------------|-----------------|-----------------|

| 01      | 8 October 2003 | First release   | Stephen Hibberd |

|         |                |                 |                 |

|         |                |                 |                 |

PIC INT\_REG\_50 ..... 14

Reserved

14

PIC\_MOD\_ ID

14

FPBC\_CTRL

15

FPBC\_ADDR

15

FPBC\_STAT

15

FPBC\_MON

17

EN\_EJT\_DSU\_APERTURE

17

14 14

#### **Programmable Source Decoder with Integrated Peripherals**

0x03 E0D8

# **Contents**

#### **PCI Configuration Registers**

| PCI Configuration Registe          | ers                                              | 0x03 E0D8 PIC<br>0x03 E0DC—EFF0 Res |

|------------------------------------|--------------------------------------------------|-------------------------------------|

| 0x0000                             | Device ID/Vendor ID4                             | 0x03 EFF4 PIC                       |

| 0x0004                             | Command/Status 4                                 | 0x03 EFF8 Res                       |

| 0x0008                             | Class Code/Revision ID 5                         | 0x03 EFFC PIC                       |

| 0x000C                             | Latency Timer/Cache Line                         | F-PI Bus Controller Registers       |

| 0x0010                             | Size5<br>Base10 Address Register5                | 0x03 F000 FPE                       |

| 0x0014                             | Base14 Address Register                          | 0x03 F00C FPE                       |

| 0x0018                             | Base 18 Address Register 6                       | 0x03 F010 FPE                       |

| 0x002C                             | Subsystem ID/Subsystem                           | 0x03 F014 FPE                       |

|                                    | Vendor ID6                                       | 0x03 F018 EN                        |

| FPI Null Module Registers          | S                                                |                                     |

| 0x00 0FFC                          | Module ID Register7                              | 0x03 F01C EN_                       |

| 0x0030                             | Reserved7                                        | 0x03 F020 MIF                       |

| 0x0034                             | Capabilities Pointer7                            | 0x03 F024 MIF                       |

| 0x003C                             | Max_Lat, Min_Gnt, Interrupt pin, Interrupt Line7 | 0x03 F028 MIF                       |

| 0x0040                             | Power Management                                 | 0x03 F02C MIF                       |

| 0,0040                             | Capabilities                                     | 0x03 F034 EN                        |

| 0x0044                             | PMCSR7                                           | 0x03 F040 SW                        |

| MIPS E-JTAG S'ware DeB             |                                                  | 0x03 F044 SW<br>0x03 F048 SW        |

| 0x03 D000                          | Implementation Register8                         | 0x03 F04C SW                        |

| <b>Priority Interrupt Controll</b> |                                                  | 0x03 FFE0 FPE                       |

| 0x03 E000                          | PIC INT PRIORITY 10                              | 0x03 FFE4 FPE                       |

| 0x03 E004                          | PIC_INT_SRC10                                    | 0x03 FFE8 FPE                       |

| 0x03 E008—E010                     | Reserved                                         | PCI-XIO Registers                   |

| 0x03 E014                          | PIC_INT_REG_110                                  | 0x04 0000 PCI                       |

| 0x03 DFFC                          | Module ID                                        | 0x03 FFEC FPE                       |

| 0x03 E018                          | PIC_INT_REG_211                                  | 0x03 FFF0—FFF8 Res                  |

| 0x03 E01C<br>0x03 E020             | PIC_INT_REG_3 11<br>PIC_INT_REG_4 11             | 0x03 FFFC FPE<br>0x04 0004 PCI      |

| 0x03 E024                          | PIC_INT_REG_511                                  | 0x04 0008 PCI                       |

| 0x03 E028                          | PIC_INT_REG_611                                  | 0x04 000C PCI                       |

| 0x03 E02C                          | PIC_INT_REG_711                                  | 0x04 0010 PCI                       |

| 0x03 E030                          | PIC_INT_REG_811                                  | 0x04 0014 PCI                       |

| 0x03 E034                          | PIC_INT_REG_9 11                                 | 0x04 0018 PCI                       |

| 0x03 E038<br>0x03 E03C             | PIC_INT_REG_10 11<br>PIC_INT_REG_11 11           | 0x04 001C PCI<br>0x04 0020 PCI      |

| 0x03 E040                          | PIC INT REG 12 12                                | 0x04 0020 PCI                       |

| 0x03 E044                          | PIC_INT_REG_13 12                                | 0x04 0028 Rea                       |

| 0x03 E048                          | PIC_INT_REG_14 12                                | 0x04 002C Ger                       |

| 0x03 E04C                          | PIC_INT_REG_15 12                                | (GF                                 |

| 0x03 E050                          | PIC_INT_REG_16 12                                | 0x04 0030 Ger                       |

| 0x03 E054<br>0x03 E058             | PIC_INT_REG_17 12<br>PIC_INT_REG_18 12           | (GF<br>0x04 0034 Ger                |

| 0x03 E05C                          | PIC_INT_REG_1912                                 | (GF                                 |

| 0x03 E060                          | PIC INT REG 20                                   | 0x04 0038 Ger                       |

| 0x03 E064                          | PIC_INT_REG_21 12                                | (GF                                 |

| 0x03 E068                          | PIC_INT_REG_2212                                 | 0x04 0040 Ima                       |

| 0x03 E06C<br>0x03 E070             | PIC_INT_REG_23 12<br>PIC_INT_REG_24 12           | 0x04 0044 Ver                       |

| 0x03 E070                          | PIC_INT_REG_2512                                 | 0x04 0048 Ima                       |

| 0x03 E078                          | PIC_INT_REG_26 12                                | ID                                  |

| 0x03 E07C                          | PIC_INT_REG_27 12                                | 0x04 004C Ima                       |

| 0x03 E080                          | PIC_INT_REG_2812                                 | Line                                |

| 0x03 E084                          | PIC_INT_REG_29 12                                | 0x04 0050 Bas                       |

| 0x03 E088<br>0x03 E08C             | PIC_INT_REG_30 13<br>PIC_INT_REG_31 13           | 0x04 0054 Bas<br>0x04 0058 Bas      |

| 0x03 E090                          | PIC INT REG 3213                                 | 0x04 006C Sub                       |

| 0x03 E094                          | PIC_INT_REG_33 13                                | Ver                                 |

| 0x03 E098                          | PIC_INT_REG_3413                                 | 0x04 0070 Res                       |

| 0x03 E09C                          | PIC_INT_REG_3513                                 | 0x04 0074 Ima                       |

| 0x03 E0A0<br>0x03 E0A4             | PIC_INT_REG_36 13<br>PIC_INT_REG_37 13           | 0x04 007C Ima                       |

| 0x03 E0A4                          | PIC INT REG 3813                                 | 0x04 007C IIIa                      |

| 0x03 E0AC                          | PIC_INT_REG_3913                                 | 0x04 0080 Ima                       |

| 0x03 E0B0                          | PIC_INT_REG_40 13                                |                                     |

| 0x03 E0B4                          | PIC_INT_REG_4113                                 | 0x04 0084 Ima                       |

| 0x03 E0B8                          | PIC_INT_REG_42 13                                |                                     |

| 0x03 E0BC<br>0x03 E0C0             | PIC_INT_REG_43 13<br>PIC_INT_REG_44 13           | 0x04 0800 DM.<br>0x04 0804 DM.      |

| 0x03 E0C0                          | PIC_INT_REG_44                                   | 0x04 0804 DM                        |

| 0x03 E0C8                          | PIC_INT_REG_4613                                 | 0x04 080C DM                        |

| 0x03 E0CC                          | PIC_INT_REG_47 13                                | 0x04 0810 XIO                       |

| 0x03 E0D0                          | PIC_INT_REG_4813                                 | 0x04 0814 XIC                       |

| 0x03 E0D4                          | PIC_INT_REG_49 14                                | 0x04 0818 XIO                       |

|                                    |                                                  |                                     |

EN\_MIPS\_EXT\_WBEMPTY PCI Interrupt Status ..... 20 FPBC\_INT\_SET 20

PCI Control

24

PCI\_Base1\_lo

24

PCI\_Base1\_hi

24

PCI\_Base1\_hi

24

PCI\_Base1\_hi

24

PCI\_Base2\_hi

25

PCI\_Base2\_hi

25

Read Data Lifetime Timer

25

Casered Purpose DCI Master

24

General Purpose PCI Master (GPPM) Write Data ..... 25 General Purpose PCI Master (GPPM) Read Data ..... 25 General Purpose PCI Master (GPPM) Control ..... 25 Image of Device ID and Vendor ID . . . . . . . . . . . . . . Image of Command/Status 26 Image of Class Code/Revision

Base Address 14 Image . .

Reserved

Base Address 18 Image . . 27 Subsystem ID/Subsystem Vendor ID Write Port .... 27

Image of Configuration Reg 34

Image of Configuration Reg 3C

Image of Configuration Reg 40

Image of Configuration Reg 44 DMA PCI Address ...... 28 DMA Internal Address ....

DMA Transfer Size . . . . . DMA Controls . . . . .

XIO Sel1 Profile .....

XIO Control Register .... 29 XIO Sel0 Profile .....

27

27

27

27

27

28

28 28

29

29

# **PNX8526**

#### Programmable Source Decoder with Integrated Peripherals

| 0x04 081C              | XIO Sel2 Profile                                       | 0x04 4030                   | Mixed Status Register (MSR)                      |

|------------------------|--------------------------------------------------------|-----------------------------|--------------------------------------------------|

| 0x04 0820              | GPXIO_address                                          |                             | 48<br>FIFO Control Register (FCR)                |

| 0x04 0824              | GPXIO_write_data 31                                    | 0x04 4030                   | FIFO Control Register (FCR)                      |

| 0x04 0828              | GPXIO_read_data31                                      | 0-04 4004                   | 48                                               |

| 0x04 082C              | GPXIO_ctrl                                             | 0x04 4034                   | UART Transmit Register                           |

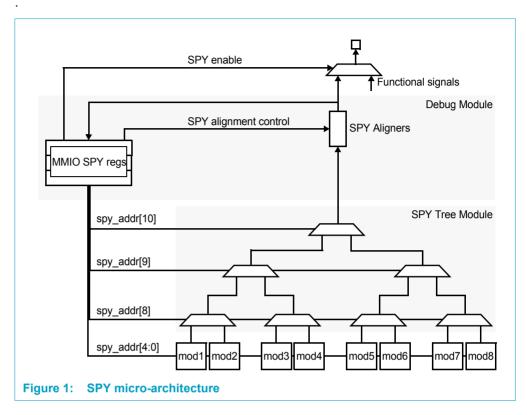

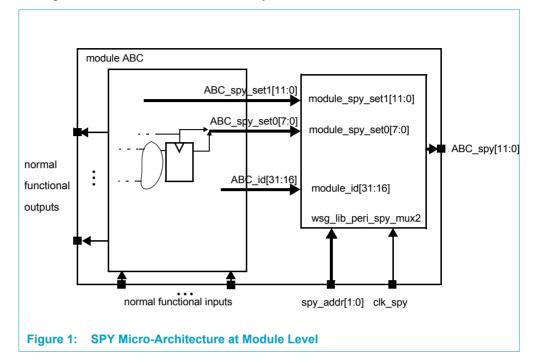

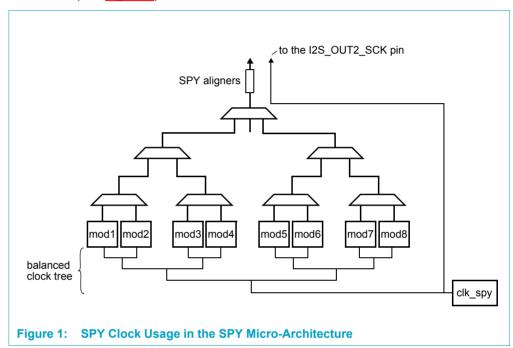

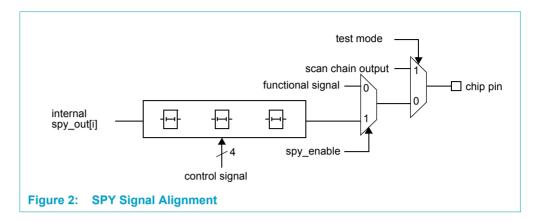

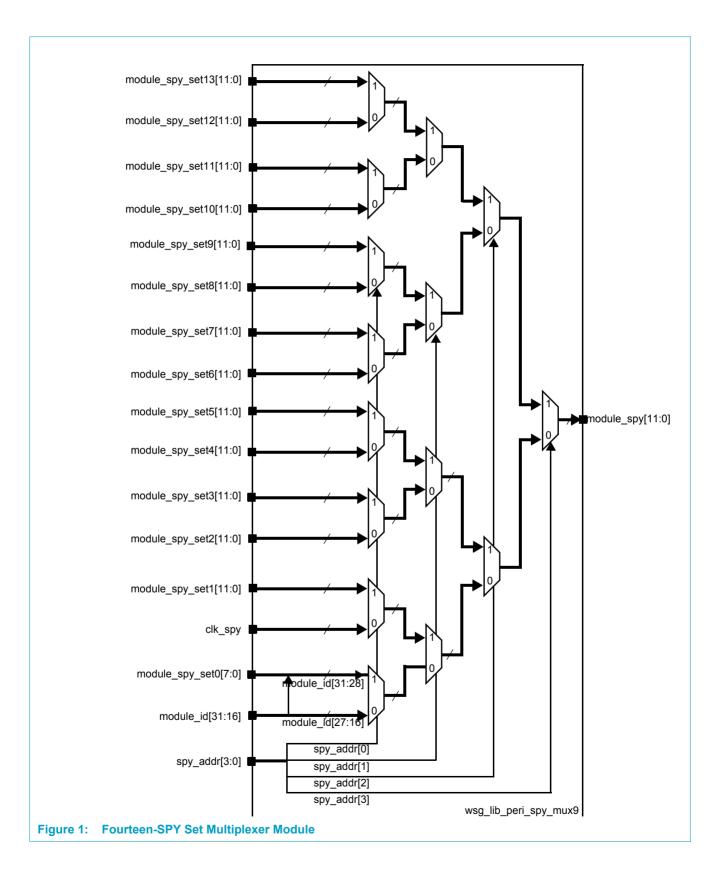

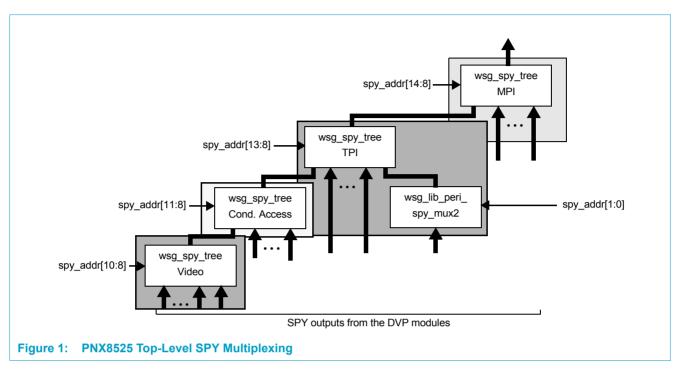

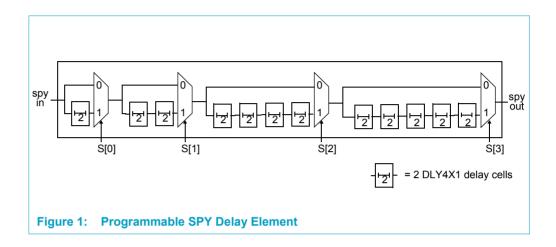

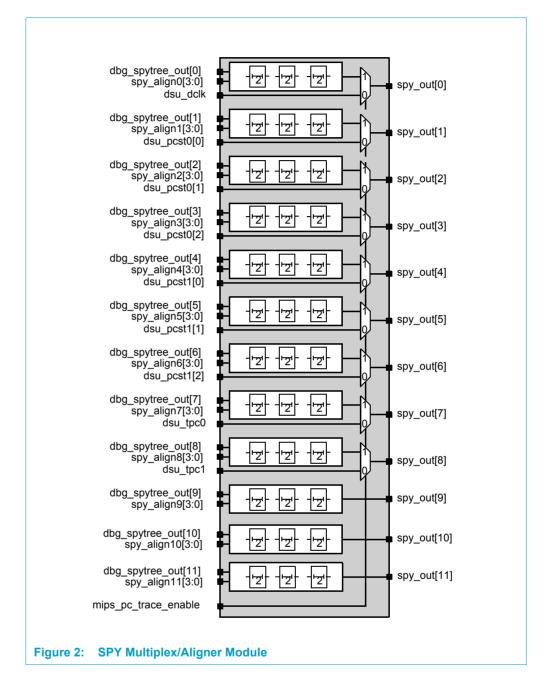

| Spy Micro-Architectur  | -                                                      | 0x04 4034                   | (UTR) 48<br>UART Receive Register (URR)          |

| 0x04 1000              | DBG_SPY_ADDR_REG32                                     |                             | 48                                               |

| 0x04 1004<br>0x04 0830 | DBG_SPY_DATA_REG32<br>NAND-Flash controls32            | 0x04 4038                   | UART Status Register (USR)                       |

| 0x04 0830<br>0x04 0FFC | Module ID                                              |                             | UART Status Register (USR)                       |

| 0x04 1008              | DBG_SPY_ALIGN_REG0.33                                  | 0x04 403C                   | DMA Write Address Register                       |

| 0x04 100C              | DBG_SPY_ALIGN_REG1.36                                  | 0x04 4040                   | (DWA)                                            |

| 0x04 1FF4              | Powerdown Register 37                                  | 0x04 4FE0                   | SCIF INT STATUS 48                               |

| 0x04 1FFC              | Module ID Register37                                   | 0x04 3FFC                   | SCIF_MODULE_ID 48                                |

| Boot Registers         |                                                        | I2C Registers               |                                                  |

| 0x04 2000<br>0x04 2FFC | Boot Status                                            | 0x04 5000                   | I2C CONTROL 49                                   |

| Smartcard UART 1 Re    | Module ID                                              | 0x04 4FE4                   | SCIF_INT_ENABLE 49                               |

|                        | -                                                      | 0x04 4FE8                   | SCIF_INT_CLEAR 49                                |

| 0x04 3000              | Reset Register (RER)38                                 | 0x04 4FEC                   | SCIF_INT_SET 49                                  |

| 0x04 3004              | Clock Configuration Register                           | 0x04 4FF4<br>0x04 4FFC      | SCIF_POWERDOWN 49                                |

| 0x04 3008              | (CCR)                                                  | 0x04 4FFC<br>0x04 5004      | SCIF_MODULE_ID 49<br>I2C DATA REGISTER 50        |

| 0,04 9000              | Register (PDR)40                                       | 0x04 5008                   | I2C STATUS REGISTER . 50                         |

| 0x04 300C              | UART Configuration Register                            | 0x04 500C                   | I2C ADDRESS REGISTER 50                          |

|                        | 2 (UCR2)                                               | 0x04 5010                   | I2C STOP REGISTER 50                             |

| 0x04 3010              | DMA Read Address Register                              | 0x04 5014                   | I2C PD REGISTER 51                               |

|                        | (DRA)                                                  | 0x04 5018                   | I2C BUS SET REGISTER 51                          |

| 0x04 3014              | Guard Time Register (GTR) 41                           | 0x04 501C                   | 12C BUS OBSERVATION                              |

| 0x04 3018              | UART Configuration Register                            |                             | REGISTER 51                                      |

| 0,04 2010              | 1 (UCR1)                                               | 0x04 5020—5FDC              | Reserved 51                                      |

| 0x04 301C              | DMA Length Register (DLR)                              | 0x04 5FE0                   | I2C INTERRUPT STATUS<br>REGISTER                 |

| 0x04 3020              | Time Out Configuration                                 | 0x04 5FE4                   | I2C INTERRUPT ENABLE                             |

|                        | Register (TOC)                                         |                             | REGISTER                                         |

| 0x04 3024              | Time Out Register 1 (TOR1)42                           | 0x04 5FE8                   | I2C INTERRUPT CLEAR                              |

| 0x04 3028              | Time Out Register 2 (TOR2)43                           |                             | REGISTER 52                                      |

| 0x04 302C              | Time Out Register 3 (TOR3)43                           | 0x04 5FEC                   | I2C INTERRUPT SET                                |

| 0x04 3030              | Mixed Status Register (MSŔ)                            | 0x04 5FF4                   | REGISTER 52<br>I2C POWERDOWN                     |

| 0x04 3030              | FIFO Control Register (FCR)                            | 0,04 51 1 4                 | REGISTER                                         |

|                        | FIFO Control Register (FCR)                            | 0x04 5FFC                   | <b>I2C MODULE ID REGISTER</b>                    |

| 0x04 3034              | UART Transmit Register                                 |                             |                                                  |

| 0.04 2024              | (UTR)                                                  | 0x04 6000                   | I2C CONTROL                                      |

| 0x04 3034              | UART Receive Register (URR)                            | 0x04 6004<br>0x04 6008      | I2C DATA REGISTER 53<br>I2C STATUS REGISTER . 53 |

| 0x04 3038              | LIART Status Register (LISR)                           | 0x04 6008                   | I2C ADDRESS REGISTER 53                          |

| 0,04 9090              | UART Status Register (USR)                             | 0x04 6010                   | I2C STOP REGISTER 53                             |

| 0x04 303C              | DMA Write Address Register                             | 0x04 6014                   | I2C PD REGISTER 53                               |

|                        | (DWA)46                                                | 0x04 6018                   | I2C BUS SET REGISTER 53                          |

| 0x04 3040              | Command Register (CRE) . 46                            | 0x04 601C                   | I2C BUS OBSERVATION                              |

| 0x04 3FE0              | SCIF_INT_STATUS 46                                     |                             | REGISTER 53                                      |

| 0x04 3FE4              | SCIF_INT_ENABLE46                                      | 0x04 6020—5FDC              | Reserved 53                                      |

| 0x04 3FE8              | SCIF_INT_CLEAR 47                                      | 0x04 6FE0                   | I2C INTERRUPT STATUS                             |

| 0x04 3FEC<br>0x04 3FF4 | SCIF_INT_SET47<br>SCIF_POWERDOWN47                     | 0x04 6FE4                   | REGISTER 53<br>I2C INTERRUPT ENABLE              |

| Smartcard UART 2 Reg   | nisters                                                |                             | REGISTER                                         |

| 0x04 4000              |                                                        | 0x04 6FE8                   | I2C INTERRUPT CLEAR                              |

| 0x04 4000<br>0x04 4004 | Reset Register (RER)48<br>Clock Configuration Register |                             | REGISTER 53                                      |

| 0,04 4004              | (CCR)                                                  | 0x04 6FEC                   | I2C INTERRUPT SET                                |

| 0x04 4008              | Programmable Divider                                   | 0x04 6FF4                   | REGISTER 53<br>I2C POWERDOWN                     |

|                        | Register (PDR)48                                       | 0004 01 1 4                 | REGISTER                                         |

| 0x04 400C              | UART Configuration Register                            | 0x04 6FFC                   | 12C MODULE ID REGISTER                           |

| 0x04 3010              | 2 (UCR2)                                               |                             |                                                  |

| 0,04 00 10             | (DRA)                                                  | Clock Registers             |                                                  |

| 0x04 4014              | Guard Time Register (GTR) 48                           | 0x04 7000                   | PLL0_CTL 53                                      |

| 0x04 4018              | UART Configuration Register                            | 0x04 7004                   | PLL1_CTL 54                                      |

|                        | 1 (UCR1)                                               | 0x04 7008                   | PLL2_CTL 54                                      |

| 0x04 401C              | DMA Length Register (DLR)                              | 0x04 700C                   | PLL3_CTL                                         |

| 0.04 4020              | Timoout Configuration                                  | 0x04 7010                   | PLL4_CTL 55<br>PLL5_CTL 55                       |

| 0x04 4020              | Timeout Configuration<br>Register (TOC)48              | 0x04 7014<br>0x04 7018      | PLL5_CTL                                         |

| 0x04 4024              | Timeout Register 1 (TOR1) 48                           | 0x04 7018<br>0x04 701C—709C | RESERVED                                         |

| 0x04 4028              | Timeout Register 2 (TOR2) 48                           | 0x04 7100                   | DDS0 ICP1 CTL 55                                 |

| 0x04 402C              | Timeout Register 3 (TOR3) 48                           | 0x04 7104                   | DDS1_ICP2_CTL 56                                 |

|                        | ,                                                      | 0x04 7108                   | DDS2_AI1_CTL 56                                  |

|                        |                                                        |                             |                                                  |

**PNX8526**

| 0x04 710C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DD3_AO1_CTL56                                                                                                                                                                                                    | 0x04 7460                                                                                                                                                                                                                                                                                                                      | CLK_OPTION_CTL 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DDS4_AI2_CTL                                                                                                                                                                                                     | 0x04 7464                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x04 7110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DDS5_A02_CTL                                                                                                                                                                                                     | 0X04 7404                                                                                                                                                                                                                                                                                                                      | MSPOUT1_CLK_SRC_CTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x04 7114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                  | 0.04 7400                                                                                                                                                                                                                                                                                                                      | MCDOUT4 OLK OT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0x04 7118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DDS6_AIO3_CTL56                                                                                                                                                                                                  | 0x04 7468                                                                                                                                                                                                                                                                                                                      | MSPOUT1_CLK_CTL 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x04 711C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DDS7_SPDO_CTL56                                                                                                                                                                                                  | 0x04 746C                                                                                                                                                                                                                                                                                                                      | MSPOUT2_CLK_SRC_CTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0x04 7120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DDS8_TSDMA_CTL56                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x04 7124—719C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RESERVED                                                                                                                                                                                                         | 0x04 7470                                                                                                                                                                                                                                                                                                                      | MSPOUT2_CLK_CTL 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0x04 7200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLK_MEM_CTL56                                                                                                                                                                                                    | 0x04 7474                                                                                                                                                                                                                                                                                                                      | CLK_1394RX_SRC_CTL . 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0x04 7204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLK FPI CTL                                                                                                                                                                                                      | 0x04 7478                                                                                                                                                                                                                                                                                                                      | CLK_1394RX_CTL 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x04 7208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reserved                                                                                                                                                                                                         | 0x04 747C                                                                                                                                                                                                                                                                                                                      | MSP2_IN_CLK_SRC_CTL 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0x04 720C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CLK TPI CTL56                                                                                                                                                                                                    | 0x04 7480                                                                                                                                                                                                                                                                                                                      | MSP2_IN_CLK_CTL 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |